Modular-Things PHY Backpacks

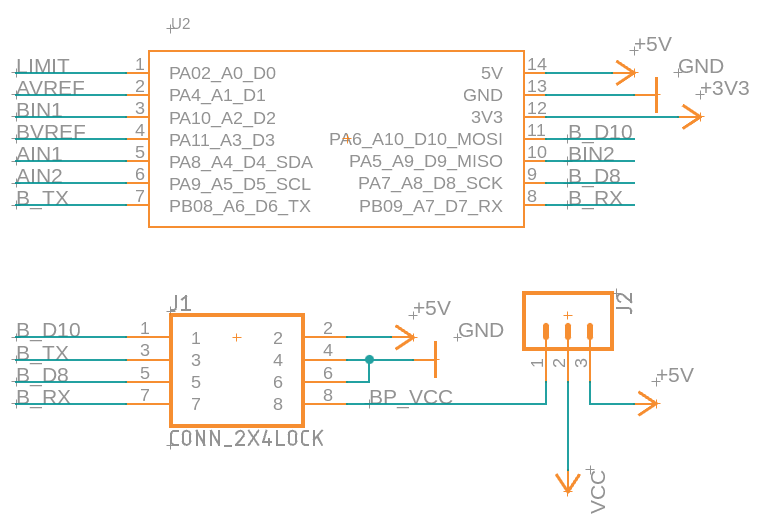

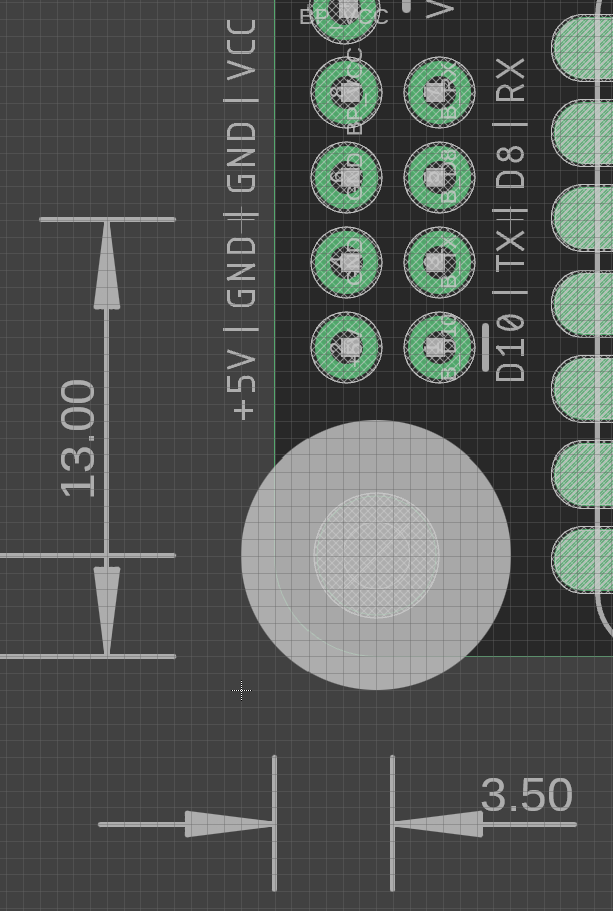

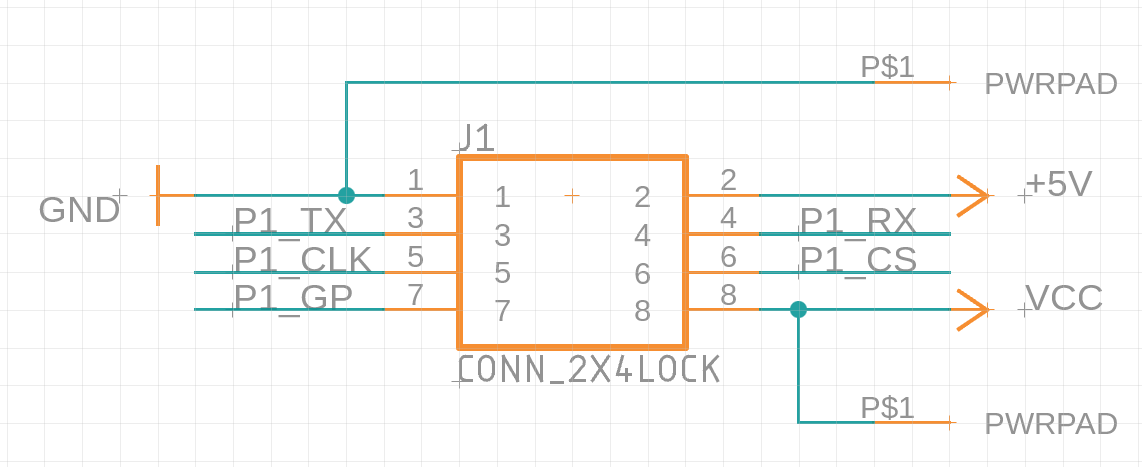

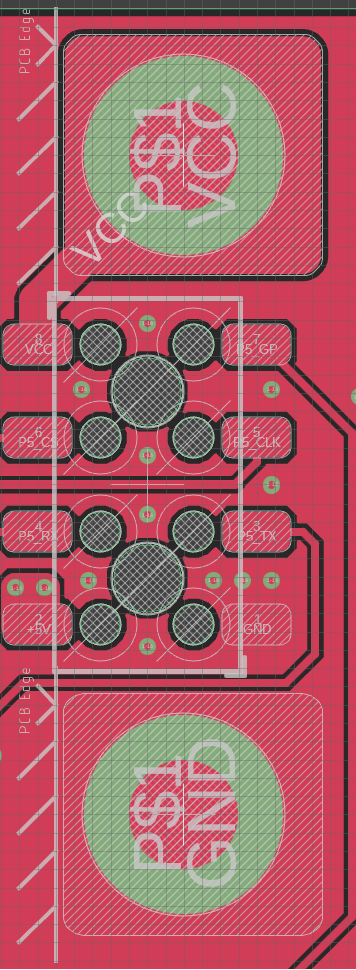

We stuck a 2x4 header on most of our XIAO-based modular-things boards, which have this layout and pinout:

|  |

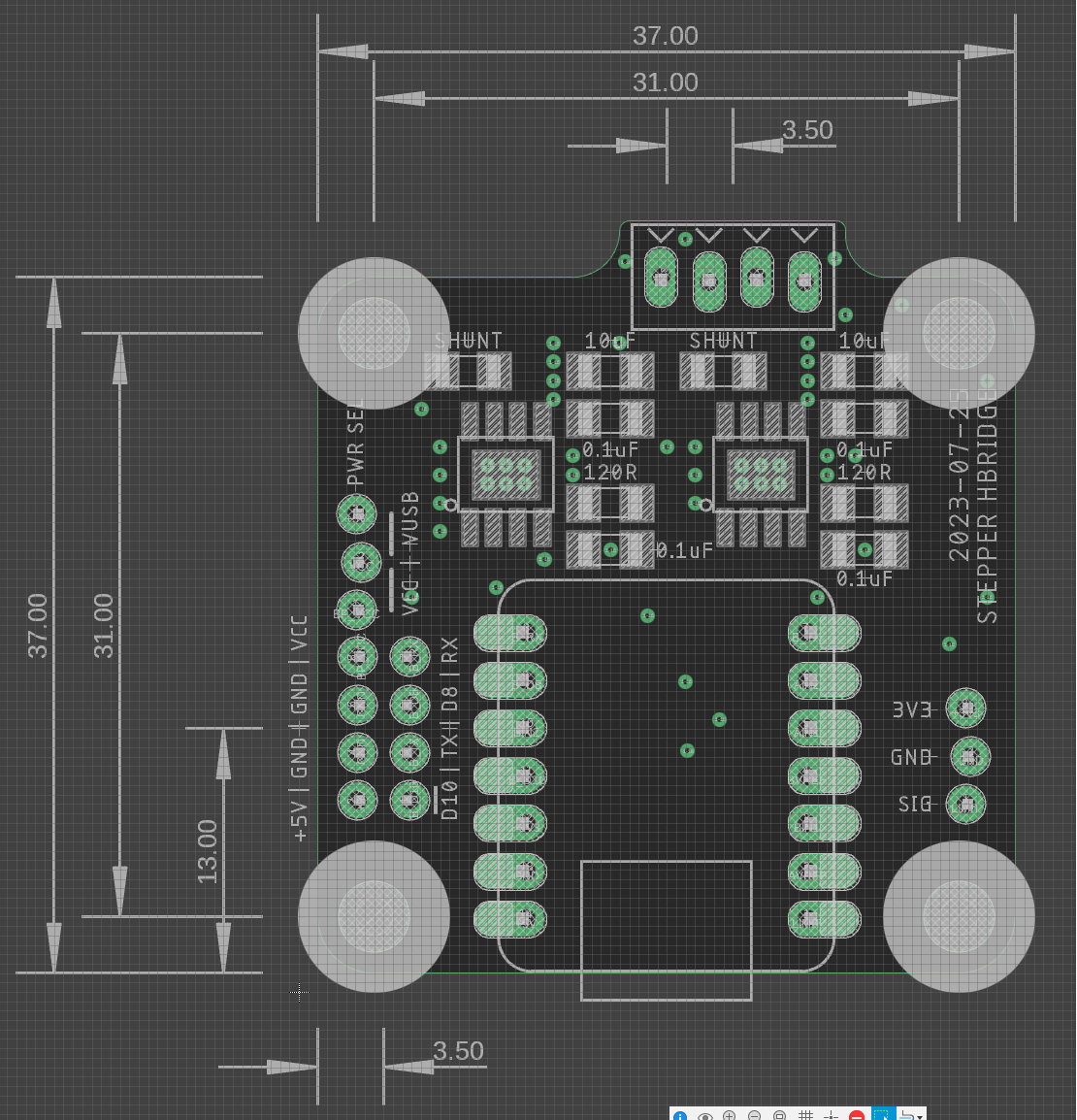

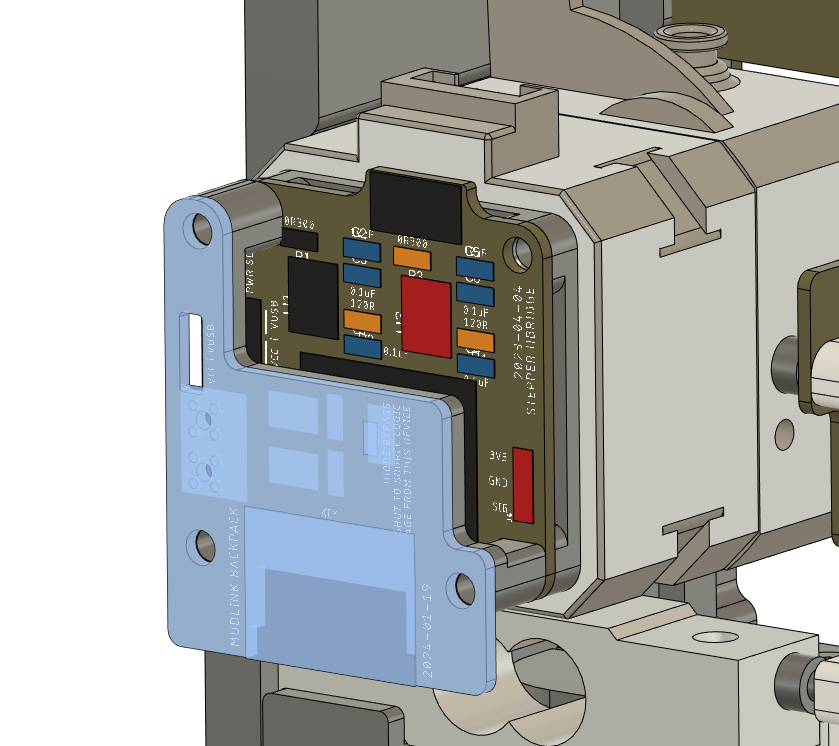

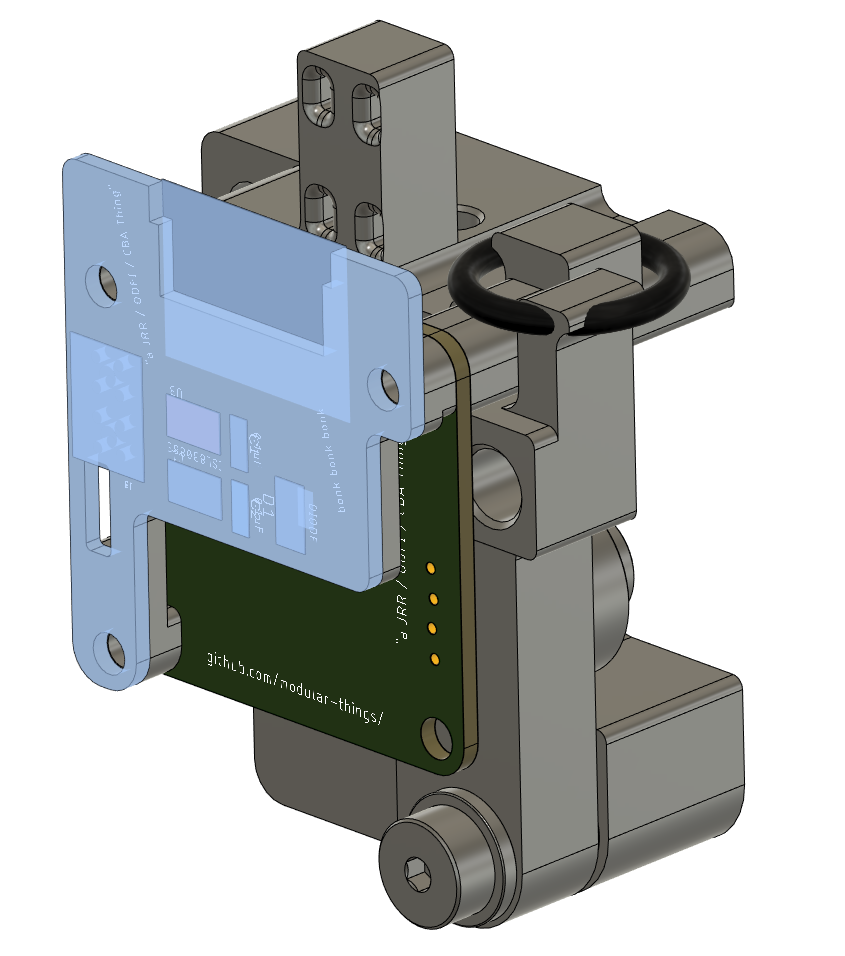

This effectively breaks out the XIAO’s UART port (TX/RX as well as two GPIO). We can then attach “backpacks” on the front or the back of the circuit:

|  |

TODO: .stl’s for mounts here…

TODO: link to circuit repo for example…

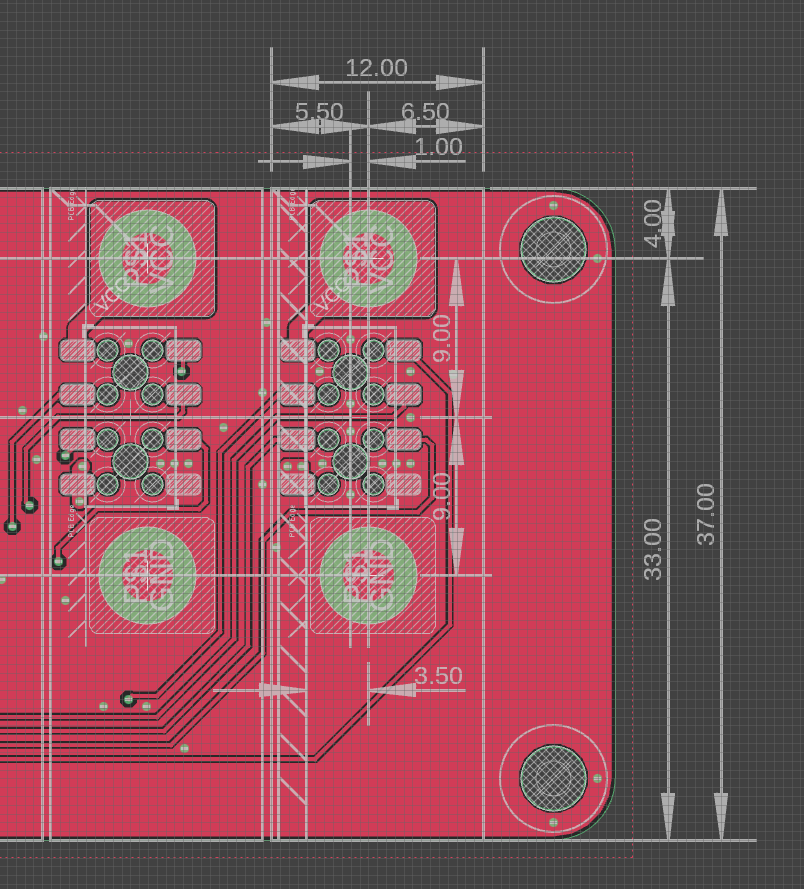

MPHY Router Slots

|  |

Slot 2x4 Pin Availabilities

| 2x4 Pin: | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| UART | GND | +5V | TX | RX | TX_EN | RX_EN | LED | VCC |

| CAN | GND | +5V | TX | RX | x | x | LED | VCC |

| SPI | GND | +5V | MOSI | MISO | SCK | CS | x | VCC |

| I2C | GND | +5V | SDA | x | SCL | x | x | VCC |

Actual Router Pinouts

| PRT | Periphs | TX/DO/SDA | RX/DI | SCK/SCL/GP1 | CS/GP2 | GP3 |

|---|---|---|---|---|---|---|

| USB0 | USB | |||||

| PRT1 | UART7, CAN3, WIRE2 | 29:TX7, 31:CTX3, 25:SDA2 | 28:RX7, 30:CRX3 | 24:SCL2 | 32:GP | 33:GP |

| PRT2 | UART2, CAN1 | 8:TX2, 22:CTX1 | 7:RX2, 23:CRX1 | 6:GP | 9:GP | 10:GP |

| PRT3 | UART1, CAN2 | 1:TX1,CTX2 | 0:RX1,CRX2 | 2:GP | 3:GP | 4:GP |

| PRT4 | UART5, SPI2 | 20:TX5, 35:MOSI2 | 21:RX5, 34:MISO2 | 37:SCK2 | 36:CS2 | 38: GP |

| PRT5 | UART3, WIRE1 | 14:TX3, 17:SDA1 | 15:RX3 | 16:SCL1 | 12:GP | 11:GP |

TODO: link to circuit repo for example…

ASIDE: ATSAMDx SERCOM Pin Mappings

| SIGGIES | PAD0 | PAD1 | PAD2 | PAD3 |

|---|---|---|---|---|

| UART | RX, TX | RX, CLK | RX, RTS | RX, CTS |

| SPI | DI, DO | DI, SCK | DI, CS | DI, DO |

| I2C | SDA | SCL | - | - |